allmightbeV2EX 第 526802 号会员,加入于 2021-01-04 17:02:26 +08:00 |

allmightbe 最近回复了

2024-01-08 00:15:31 +08:00 回复了 allmightbe 创建的主题 › 程序员 › 为什么 uart 两个数据帧之间必须有空闲位? |

@swulling

如果发送端连续发送数据,没有空闲期,两位高电平的停止位后立刻传输下一次的起始位。那么接收端怎么区分启动位,停止位,与数据位?

答:连续数据没法区分帧结构。一步错 步步错。(原话是这么说的,连续数据没法区分帧结构。我以为这就是再说必须要有空闲位😂,原来是我理解错了吗)

如果发送端连续发送数据,没有空闲期,两位高电平的停止位后立刻传输下一次的起始位。那么接收端怎么区分启动位,停止位,与数据位?

答:连续数据没法区分帧结构。一步错 步步错。(原话是这么说的,连续数据没法区分帧结构。我以为这就是再说必须要有空闲位😂,原来是我理解错了吗)

2023-10-05 17:43:48 +08:00 回复了 allmightbe 创建的主题 › 程序员 › DDR 的交织原理有点不理解? |

2023-10-05 17:42:36 +08:00 回复了 allmightbe 创建的主题 › 程序员 › DDR 的交织原理有点不理解? |

@Ayahuasec #2

我见过的比较多的设计是按 Row-Column-Bank 去编址的。

-------

对于这个地址交织,这个我是明确的:就是 row 必须在 col 左边。但至于 bank 到底放到哪里,这个有什么说法吗?

https://imgur.com/bGKe6le.png

看了一个视频,里面是这么放的:

- 因为访问一般是 4 字节对齐的,所以 col 的低 2bit 放最右边。

- 然后接着放 bank 的 2bit ,这样可以利用到 bank 之间的独立性

- 然后放 col 的高 1bit ,这样一轮循环后,使得 col 地址变成 1 时,就可以利用到 row hit 的高效率了。

不知道这么理解对不对。

我见过的比较多的设计是按 Row-Column-Bank 去编址的。

-------

对于这个地址交织,这个我是明确的:就是 row 必须在 col 左边。但至于 bank 到底放到哪里,这个有什么说法吗?

https://imgur.com/bGKe6le.png

看了一个视频,里面是这么放的:

- 因为访问一般是 4 字节对齐的,所以 col 的低 2bit 放最右边。

- 然后接着放 bank 的 2bit ,这样可以利用到 bank 之间的独立性

- 然后放 col 的高 1bit ,这样一轮循环后,使得 col 地址变成 1 时,就可以利用到 row hit 的高效率了。

不知道这么理解对不对。

2023-10-04 18:46:43 +08:00 回复了 allmightbe 创建的主题 › 程序员 › DDR 的交织原理有点不理解? |

2023-10-04 18:42:09 +08:00 回复了 allmightbe 创建的主题 › 程序员 › DDR 的交织原理有点不理解? |

@liwufan #13

是我蠢了。我理解这个 Decoder 的意思了。因为每行有 1024x4 的数据,所以下面那个粗箭头,需要有 4096 根来分别选中它们。

视频我又看了一遍,那我理解 下面那个粗箭头,应该就是 1024x4 的宽度(要把括号里的 x4 乘进去)。毕竟都叫 bit line 了。

视频我是看了,只是我是 最开始,当时那一遍没太看懂。后面这两天 又看了好多乱七八糟文档文章。

是我蠢了。我理解这个 Decoder 的意思了。因为每行有 1024x4 的数据,所以下面那个粗箭头,需要有 4096 根来分别选中它们。

视频我又看了一遍,那我理解 下面那个粗箭头,应该就是 1024x4 的宽度(要把括号里的 x4 乘进去)。毕竟都叫 bit line 了。

视频我是看了,只是我是 最开始,当时那一遍没太看懂。后面这两天 又看了好多乱七八糟文档文章。

2023-10-04 17:53:22 +08:00 回复了 allmightbe 创建的主题 › 程序员 › DDR 的交织原理有点不理解? |

2023-10-04 17:41:58 +08:00 回复了 allmightbe 创建的主题 › 程序员 › DDR 的交织原理有点不理解? |

@liwufan

@Ayahuasec

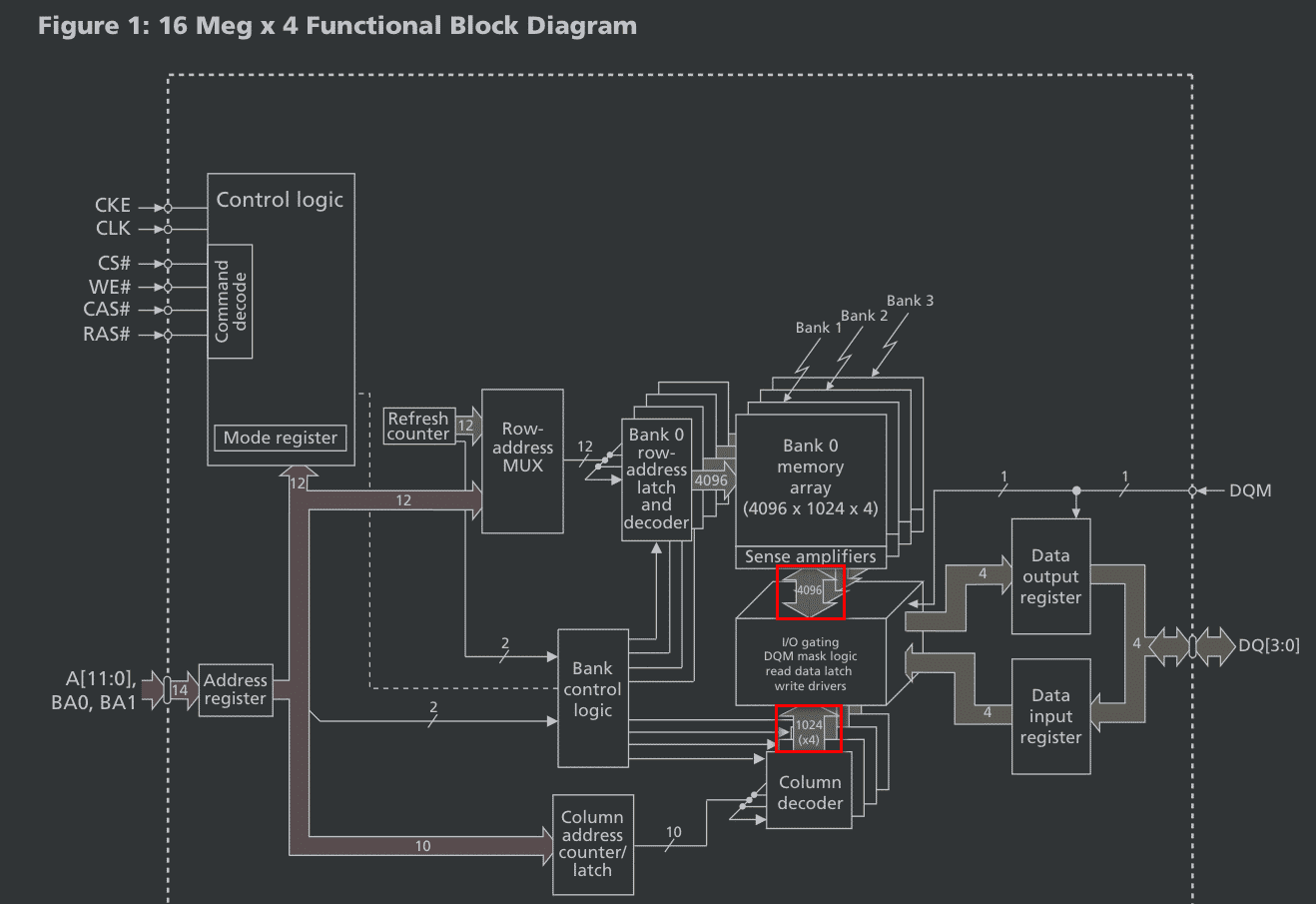

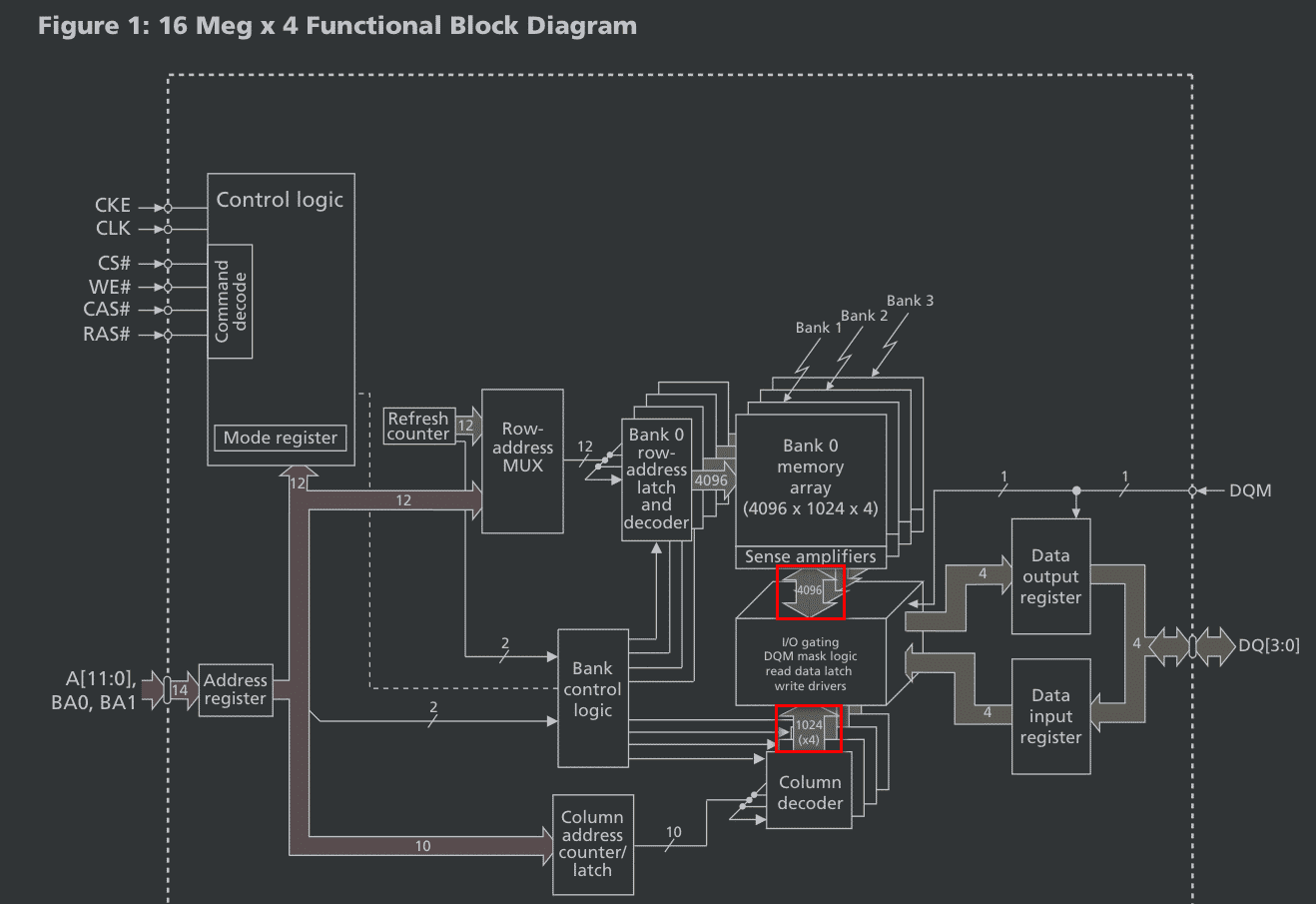

不过,micron 的 block 图里面,有一个地方不是太懂了。

就是上图的两个粗箭头。

上面那个粗箭头,我是理解的:从 row line 选中一行后,就会输出 1024 x 4 的 data 出来,所以和这个粗箭头是 1024 x 4=4096 宽。

- 粗箭头,我理解是代表这个接口处的线很多。上面的粗箭头,则有 4096 根线。

但下面那个粗箭头,就不是很理解了:

- 本身它是个粗箭头,我就不是很理解。这里,我理解是为了选择确认某一 col ,那也是 10 根线,就可以了。

- 另外,这个粗箭头,到底是 1024 的宽度,还是 1024x4 的宽度呢?(就是那个括号里的 x4 要算上吗)

PS:不知道这个 block 图和实际硬件设计,是否能完全关联起来。也许这个粗箭头,只是一个逻辑上的概念。

@Ayahuasec

不过,micron 的 block 图里面,有一个地方不是太懂了。

就是上图的两个粗箭头。

上面那个粗箭头,我是理解的:从 row line 选中一行后,就会输出 1024 x 4 的 data 出来,所以和这个粗箭头是 1024 x 4=4096 宽。

- 粗箭头,我理解是代表这个接口处的线很多。上面的粗箭头,则有 4096 根线。

但下面那个粗箭头,就不是很理解了:

- 本身它是个粗箭头,我就不是很理解。这里,我理解是为了选择确认某一 col ,那也是 10 根线,就可以了。

- 另外,这个粗箭头,到底是 1024 的宽度,还是 1024x4 的宽度呢?(就是那个括号里的 x4 要算上吗)

PS:不知道这个 block 图和实际硬件设计,是否能完全关联起来。也许这个粗箭头,只是一个逻辑上的概念。

2023-10-04 17:33:09 +08:00 回复了 allmightbe 创建的主题 › 程序员 › DDR 的交织原理有点不理解? |

2023-10-04 12:56:37 +08:00 回复了 allmightbe 创建的主题 › 程序员 › DDR 的交织原理有点不理解? |

2023-10-04 12:44:47 +08:00 回复了 allmightbe 创建的主题 › 程序员 › DDR 的交织原理有点不理解? |

@liwufan #4

@Ayahuasec #5

这篇文章 https://depletionmode.com/ram-mapping.html 讲的东西我稍微总结一下:

一个内存条是一个 module ,一个 module 有两面,一面就是一个 rank 。

一个 rank 上面有 8 个 chip (也就是有 8 个 黑色长方形坨坨,人眼能看到的)

一个 chip 里面,有 4 个 bank 。

它就是强调,一个地址转到了 DDR 控制器这边以后,没有用地址的部分 bit 来定位到某个 chip 上去(相反,比如会用 部分 bit 来定位到某个 row ),相反,这个地址线 连接到所有的 chip 上面去了,那么也就是说,所有 chip 都会根据地址线的信息 来返回数据。

然后地址线发送了一个地址以后,这个地址送给了所有 chip (文中是 8 个 chip ),然后 8 个 chip 都返回了 data 。

所以,最后 DDR 就一次性 返回了 8 个字节。

根据大佬的回答,和我看网上的文章。它说的这个 技术,应该不是 prefetch ,因为 prefetch 是发生在 bank 内部的,而文章说的事情,是发生在 某个 rank 上的所有 chip 上的。

PS:不排除这个作者说的东西,是有问题的。因为别的文章没有提到过。

@Ayahuasec #5

这篇文章 https://depletionmode.com/ram-mapping.html 讲的东西我稍微总结一下:

一个内存条是一个 module ,一个 module 有两面,一面就是一个 rank 。

一个 rank 上面有 8 个 chip (也就是有 8 个 黑色长方形坨坨,人眼能看到的)

一个 chip 里面,有 4 个 bank 。

它就是强调,一个地址转到了 DDR 控制器这边以后,没有用地址的部分 bit 来定位到某个 chip 上去(相反,比如会用 部分 bit 来定位到某个 row ),相反,这个地址线 连接到所有的 chip 上面去了,那么也就是说,所有 chip 都会根据地址线的信息 来返回数据。

然后地址线发送了一个地址以后,这个地址送给了所有 chip (文中是 8 个 chip ),然后 8 个 chip 都返回了 data 。

所以,最后 DDR 就一次性 返回了 8 个字节。

根据大佬的回答,和我看网上的文章。它说的这个 技术,应该不是 prefetch ,因为 prefetch 是发生在 bank 内部的,而文章说的事情,是发生在 某个 rank 上的所有 chip 上的。

PS:不排除这个作者说的东西,是有问题的。因为别的文章没有提到过。